“Muchas veces es difícil, no siempre sale a la primera pero, cuando aciertas, sabes que acabas de hacer algo que quizás a nadie se le había ocurrido”, comparte Moises García, quien por cuarta vez en su carrera como investigador, colaboró en una nueva patente compuesta de tecnologías de compuertas lógicas.

"Método y circuito para integrar una matriz programable en campo de compuertas lógicas reconfigurables que emplean un sistema no lineal y un recableado programable eficaz" es el resultado de 1 año trabajo junto su equipo de investigadores.

Moises destaca en su ramo como investigador nivel I en el SNI (Sistema Nacional de Investigadores), miembro del IPICYT (Instituto Potosino de Investigación Científica y Tecnológica) y director de la carrera en Mecatrónica del Tec de Monterrey campus San Luis Potosí.

"Aún sigo estando contento de pensar que lo logramos"

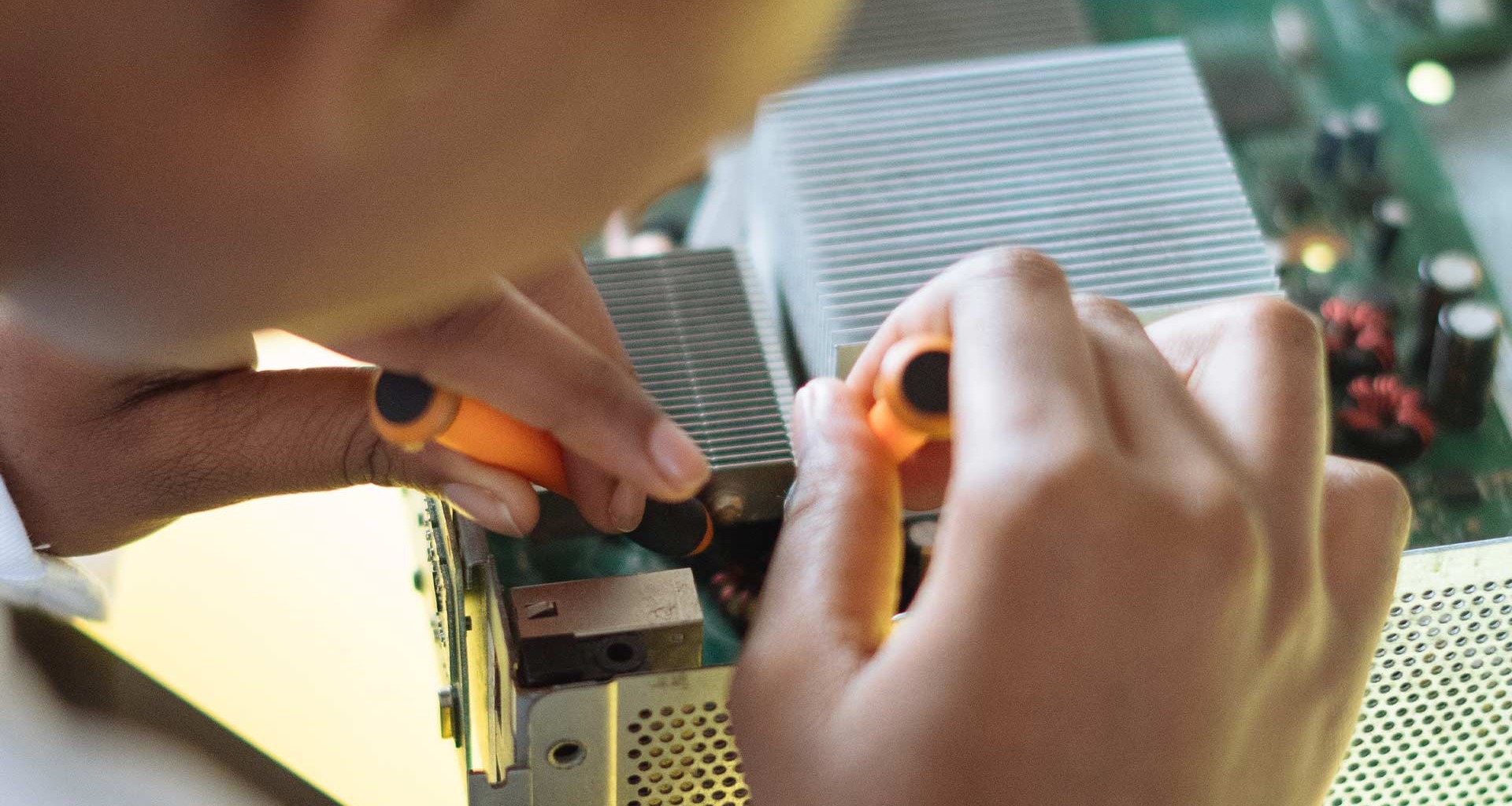

Los FPGA (Field Programmable Gate Arrays), son dispositivos programables con un lenguaje de descripción que encontramos en muchos de los aparatos electrónicos que usamos comúnmente, como reproductores de DVD hasta algunos automóviles.

Estos contienen miles de celdas conformadas de compuertas que hacen sus operaciones lógicas. De acuerdo al comportamiento de estos dispositivos, solo una en cada 8 compuertas operan.

Moises García, Eric Campos, y Roberto Rivera, lograron mejorar el rendimiento de estos FPGA con su investigación y creación de prototipo. "Aún sigo estando contento de pensar que lo logramos", cuenta el profesor de la escuela de Ingeniería.

La ciencia detrás del proyecto

En este prototipo, se optimiza la arquitectura diseñada en las celdas y compuertas lógicas por medio de una programación especializada.

En lugar de tener en cada celda 8 compuertas lógicas, solo existe una que se comporta como todas las restantes. Con ello, no solo optimizan el diseño de las celdas, sino que mejoran el funcionamiento de los FPGA en un 100%.

La invención reduce el espacio de fabricación, pues en lugar de necesitar miles de celdas en el dispositivo, solo se tendrá una que actúe como todas, beneficiando a la industria electrónica de consumo.

Nació para innovar

Como profesor investigador, Moises cuenta con una gran trayectoria. Con esta innovación aprobada para su patente, ya forma parte de su catálogo de cuatro invenciones, 2 son patentes nacionales y 2 internacionales.

“Es siempre un orgullo poder seguir descubriendo y cambiando el rumbo de la tecnología”.

“Es siempre un orgullo poder seguir descubriendo y cambiando el rumbo de la tecnología, porque nunca acabas de conocer más cosas de las cuales puedes ser parte”, comparte el profesor del campus San Luis.

SEGURO QUERRÁS LEER TAMBIÉN: